集成電路(IC)版圖設計是將電路邏輯轉化為可在硅片上制造的物理幾何圖形的關鍵過程,其本身就是一個高度復雜且依賴于先進軟件的工程實踐。從某種意義上說,現代版圖設計就是一個特定領域的、軟硬件深度結合的“軟件開發”過程。本文將剖析其核心組成,并梳理關鍵步驟,同時對比傳統軟件開發的異同。

一、核心組成:設計流程的支柱

- 設計輸入與電路網表:這是版圖設計的“源代碼”。通常由硬件描述語言(如Verilog、VHDL)編寫,經過邏輯綜合后生成門級網表。它定義了電路的功能、模塊連接關系(拓撲結構)和時序約束,相當于軟件的需求規格和架構設計文檔。

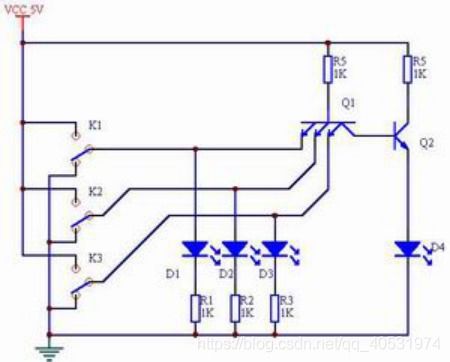

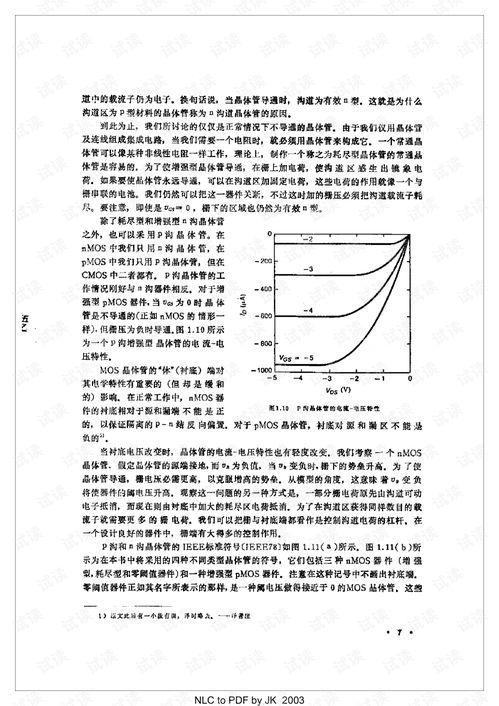

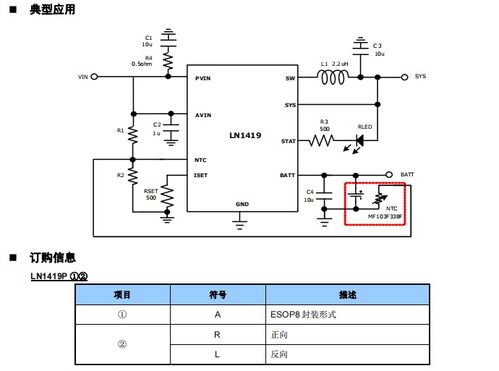

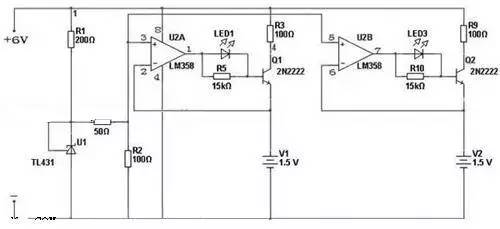

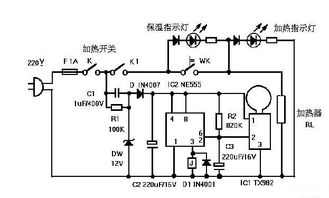

- 庫單元與工藝文件:這是版圖設計的“SDK”和“運行環境”。標準單元庫(如反相器、與非門、觸發器等)提供了預先設計好并經過工藝驗證的物理版圖單元。工藝設計套件(PDK)則提供了制造工藝的所有規則文件(如設計規則檢查DRC、版圖與電路圖對照LVS)、器件模型和物理層信息。沒有它們,設計將無法進行。

- 版圖設計工具(EDA軟件):這是核心的“集成開發環境(IDE)”。包括自動布局布線(APR)工具、手動版圖編輯器、物理驗證工具(DRC/LVS/ERC)、寄生參數提取工具以及時序/功耗分析工具等。這些軟件的質量和自動化水平直接決定了設計效率與成敗。

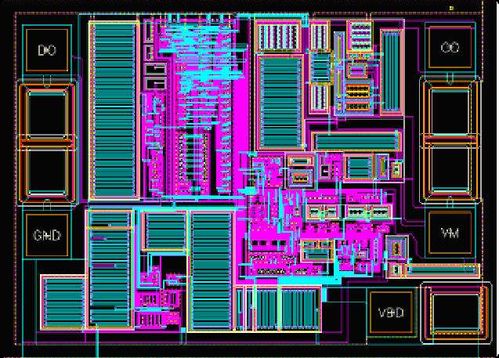

- 物理版圖數據:這是最終的“可執行文件”或“構建產物”。通常以GDSII或OASIS等標準格式存在,包含了所有層的幾何圖形信息,可直接發送給芯片制造廠(Foundry)進行光罩制作和流片。

二、關鍵步驟:從邏輯到物理的“編譯與構建”流程

版圖設計流程遵循一個高度結構化的順序,與軟件開發的構建流水線有諸多相似之處。

步驟1:規劃與布局規劃

- 類比:軟件系統架構與模塊劃分。

- 內容:根據芯片尺寸、功耗、性能目標,進行整體版圖規劃。確定核心模塊、存儲器、I/O接口等宏模塊的擺放位置,規劃電源/地網絡和全局時鐘樹的分布。這決定了后續布線的可行性和最終性能。

步驟2:布局

- 類比:將函數和類分配到具體的代碼文件和組織結構中。

- 內容:將網表中的所有標準單元和宏模塊放置在芯片的特定物理位置上。目標是優化線長、減少擁擠、滿足時序要求。現代設計主要依靠自動布局工具,但關鍵模塊可能需要手動干預。

步驟3:時鐘樹綜合

- 類比:設計并實現系統的關鍵同步機制或消息總線。

- 內容:構建一個低偏斜、低功耗的全局時鐘分布網絡,確保時鐘信號能夠幾乎同時到達所有時序單元。這是保證芯片在高頻下穩定工作的關鍵。

步驟4:布線

- 類比:實現函數和模塊之間的調用關系與數據接口連接。

- 內容:在單元之間連接金屬線,實現電路網表指定的所有電氣連接。需遵循復雜的設計規則(線寬、間距、通孔規則等),并優化信號完整性、串擾和延遲。通常分全局布線和詳細布線兩步。

步驟5:物理驗證與參數提取

- 類比:代碼的靜態檢查、編譯和動態分析。

- 內容:

- DRC:檢查版圖是否符合制造工藝的物理規則,確保可制造性。

- LVS:確保物理版圖與原始電路網表在電氣連接上完全一致,防止“編譯”錯誤。

- 寄生參數提取:從完成的版圖中提取導線帶來的電阻、電容等寄生效應,生成帶寄生參數的仿真網表。

步驟6:后仿真與簽核

- 類比:系統集成測試與發布前的最終驗證。

- 內容:利用提取的寄生參數進行包含實際物理延遲的時序分析、功耗分析和信號完整性分析。只有所有指標(時序、功耗、面積、可靠性)均滿足預設目標,設計才能“簽核”,進入制造階段。

三、與軟件開發的協同與差異

協同性:

- 高度依賴工具鏈:如同軟件開發依賴編譯器、調試器,版圖設計完全由EDA工具鏈驅動。

- 迭代與調試:版圖設計是一個“設計-驗證-修改”的快速迭代過程,與軟件開發中的調試周期類似。

- 版本管理:同樣需要使用Git等系統對設計文件(網表、約束、腳本)進行嚴格的版本控制。

- 團隊協作:大型芯片設計需要多個團隊(前端、后端、驗證)像軟件項目一樣并行協作。

關鍵差異:

- 物理約束的剛性:軟件開發邏輯靈活,而版圖設計必須服從不可妥協的物理定律和制造規則(納米尺度效應、熱效應等)。

- 極高的試錯成本:軟件可以快速迭代發布補丁,但芯片流片成本極其高昂,一次失敗可能導致巨大損失,因此驗證必須極其完備。

- 多維優化目標:需要在性能(速度)、功耗、面積(成本)這三個相互制約的維度上進行艱難的權衡優化,即所謂的PPA權衡。

結論

集成電路版圖設計是一個將抽象電路邏輯“編譯”為精密物理實體的復雜過程。其核心組成——設計數據、工藝庫和EDA工具,共同支撐起從規劃到簽核的嚴格步驟流。盡管它在物理層面上面臨著軟件開發所沒有的嚴峻約束,但其工程方法論、對自動化工具的依賴以及團隊協作模式,與先進的軟件開發實踐高度相通。理解這種“硬件實現中的軟件開發”邏輯,對于駕馭現代芯片設計至關重要。